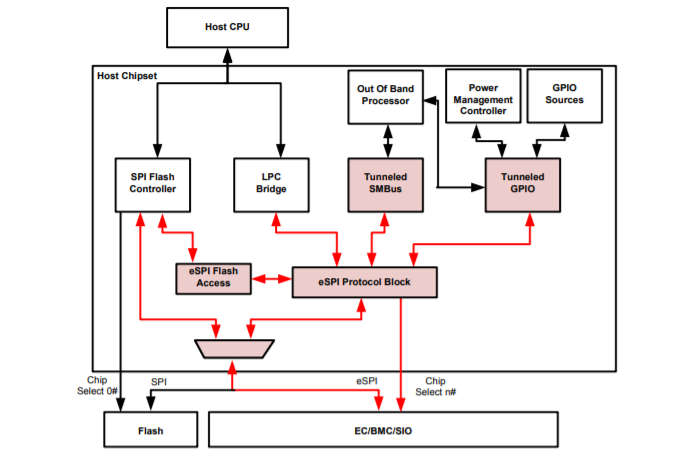

Interfaz periférica serie mejorada (eSPI)

El líder del sector Intel define la nueva norma eSPI como mejorar las transacciones de datos con un menor consumo de energía y menores costes. Los fabricantes pueden integrarlo fácilmente -a nivel de chip, placa y sistema- en sus productos.

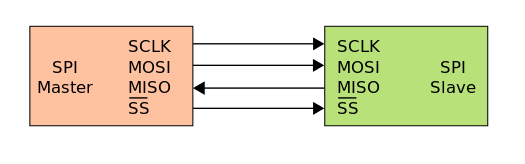

Base SPI

Los dispositivos SPI se comunican en modo dúplex completo utilizando una arquitectura maestro-esclavo (terminología alternativa como lenguaje principal y secundario) con un único maestro. El dispositivo maestro crea la trama para leer y escribir. Se admiten varios dispositivos esclavos seleccionando líneas individuales de selección de esclavo (SS), a veces llamadas líneas de selección de chip (CS).

Funciones

En total, las funciones incluyen una interfaz de cuatro hilos (recepción, transmisión, reloj y selección de esclavo) y tres configuraciones:

- IO simple (o IO estándar): Reloj, Chip-select, Señal de datos unidireccional (MOSI), Señal de datos unidireccional (MISO)

- IO DUAL: Reloj, Chip-select, Señal de datos bidireccional (IO0), Señal de datos bidireccional (IO1)

- IO QUAD: Reloj, Chip-select, Señal de datos bidireccional (IO0), Señal de datos bidireccional (IO1), Señal de datos bidireccional (IO0=2), Señal de datos bidireccional (IO3)

eSPI: ¿Qué ventajas tiene sobre otros sistemas de bus?

Con su nivel de tensión significativamente más bajo, de 1,8 V a 3,3 V, su bajo número de patillas y su frecuencia de funcionamiento dos veces más rápida, de 66 MHz frente a 33 MHz, los avances técnicos de la nueva norma eSPI son enormes. Debido a estas ventajas técnicas, eSPI pretende sustituir a la interfaz LPC (menor número de patillas), que se utiliza en el mercado informático desde hace más de 15 años y se considera el estándar común.

El menor nivel de señal reduce la potencia necesaria. También suprime el ruido de señal que suele producirse a velocidades de reloj más altas. El menor número de pines reduce el número de trazas necesarias en la placa de circuito impreso. eSPI requiere un máximo de 8 pines para un esclavo: selección de chip, reloj, 4 líneas de datos, alarma (opcional) y reinicio.

La velocidad de reloj acelerada permite un mayor ancho de banda para la transferencia de datos y operaciones más rápidas: 4x 66 MHz.

Para cumplir los requisitos del producto, los diseñadores de sistemas pueden seleccionar la velocidad de reloj máxima que admiten: 20, 25, 33, 50 o 66 MHz.

Con la estabilidad de un estándar definido para toda la industria, el eSPI puede soportar el desarrollo futuro de plataformas cliente y servidor, incluidos los periféricos y la memoria, durante muchos años.

solución de Análisis de Protocolos eSPI

2.550,00 €*

En stock, tiempo de entrega: 1 -3 días