Descripción

El analizador lógico PGY-LA-EMBD es el primer analizador lógico del sector que permite solucionar problemas de temporización y analizar simultáneamente protocolos I2C, SPI, UART, I3C, SPMI, CAN/CAN FD y RFFE en diseños embebidos. Esto te permite solucionar rápidamente problemas a nivel de circuito y de sistema. Esto te permite depurar rápidamente problemas a nivel de circuito y de sistema.

El PGY-LA-EMBD proporciona adquisición de datos asíncrona a 1GS/segundo (temporización) y adquisición de datos síncrona a 100MHz (estado), lo que lo convierte en una herramienta de depuración ideal para resolver problemas de diseño digital. Ahora los diseñadores pueden analizar rápidamente problemas de tiempo de preparación y retención, fallos y actividad de datos síncronos, además de analizar problemas de protocolo.

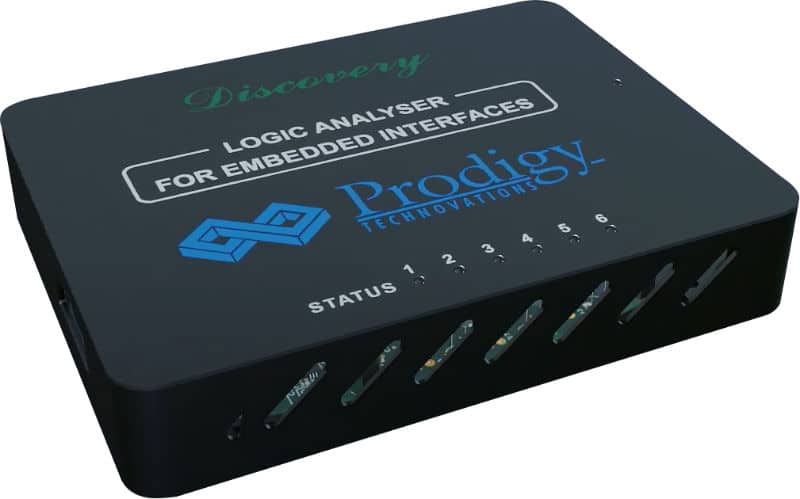

El Analizador Lógico es un analizador lógico basado en PC diseñado para profesionales exigentes. El Discovery Logic Analyser es ideal para solucionar problemas de sistemas embebidos. El analizador lógico tiene un tamaño muy reducido, por lo que puede utilizarse para solucionar problemas en aplicaciones móviles. Las funciones de descodificación de protocolos están diseñadas para solucionar problemas lógicos y de protocolos para equipos de diseño de sistemas embebidos en los mercados de consumo, industrial, domótico, sanitario y educativo.

Los diseñadores de sistemas embebidos necesitan recoger y procesar datos de múltiples interfaces como 2C, SPI, UART, I3C, SPMI, CAN/CAN FD y RFFE para desarrollar una placa embebida de alto rendimiento. El PGY-LA-EMBD descodifica los buses y muestra la actividad del protocolo con información de fecha y hora. Por tanto, es una herramienta ideal para depurar problemas de integración de hardware y software embebido y optimizar el rendimiento del software.

Los marcadores múltiples permiten realizar mediciones delta innovadoras que son fundamentales para los desarrolladores. La función de zoom permite al usuario ver áreas específicas de la señal.

Características Analizador lógico

- 16 canales con función de análisis lógico y de protocolo.

- 1GS/seg. Análisis de temporización (asíncrono)

- análisis de estado a 100 MHz (síncrono)

- Análisis simultáneo de protocolos I2C-SPI-UART-I3C-SPMI, CAN/CAN FD, y RFFE.

- Funciones de disparo detalladas: Auto, patrón, detección de protocolo (I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE) y temporización (disparo por ancho de pulso y retardo).

- Transmisión inteligente de datos del protocolo. Analizador al ordenador central para la adquisición a largo plazo a través de la interfaz USB3.0.

- Interfaz gráfica de usuario innovadora y fácil de usar.

- Análisis de errores del paquete de protocolo

- Proporciona vistas de temporización, forma de onda, listado y protocolo

- Función de filtro detallada para los datos decodificados por protocolo

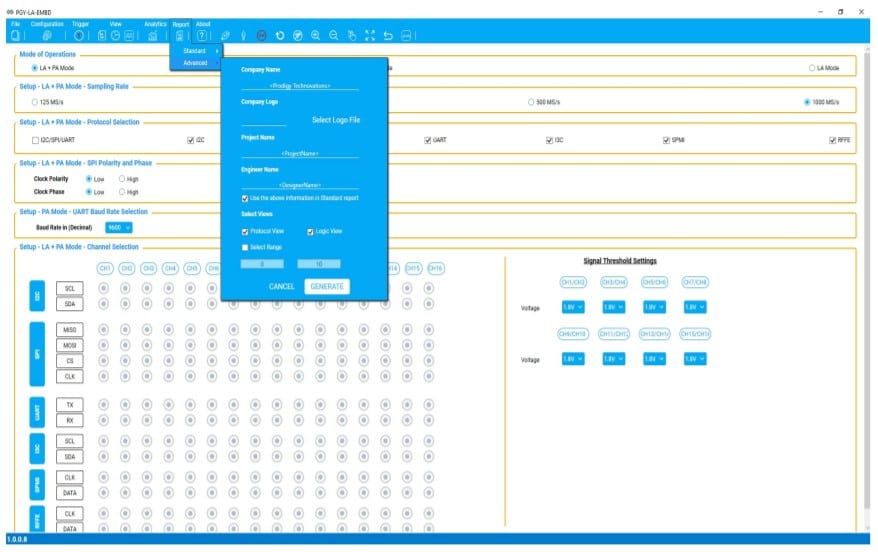

- Formato de informe PDF y CSV.

- Compatible con API.

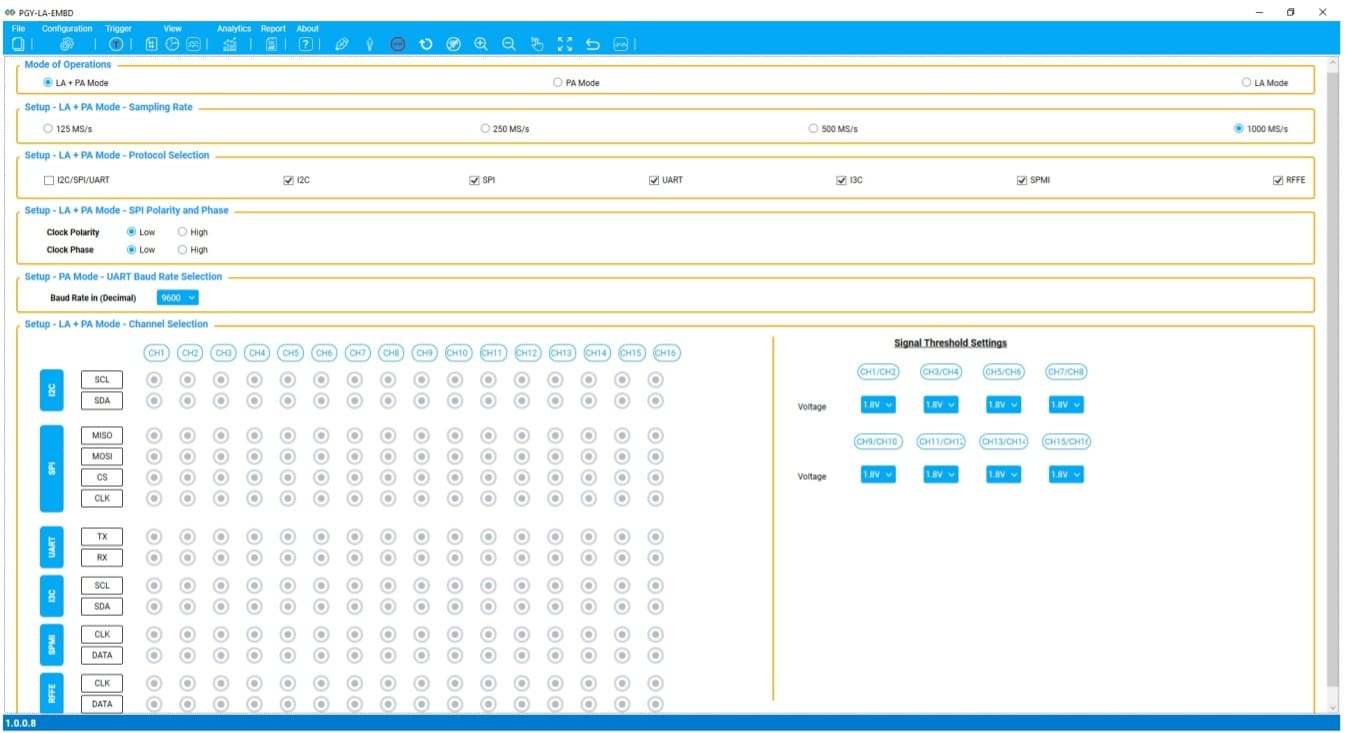

Fácil configuración

Los usuarios pueden configurar fácilmente el Analizador Lógico para Interfaces Embebidas seleccionando el modo Análisis Lógico (LA) o Análisis de Protocolos (PA) o un modo combinado (LA+PA). Esto permite una configuración rápida y sencilla del producto y la investigación de problemas complejos a nivel de sistema, ya sea en análisis lógico (análisis de estado, análisis de temporización) o decodificación de protocolos, o ambos. La función de guardar y recuperar garantiza que los desarrolladores puedan recuperar sus detalles de configuración personalizados.

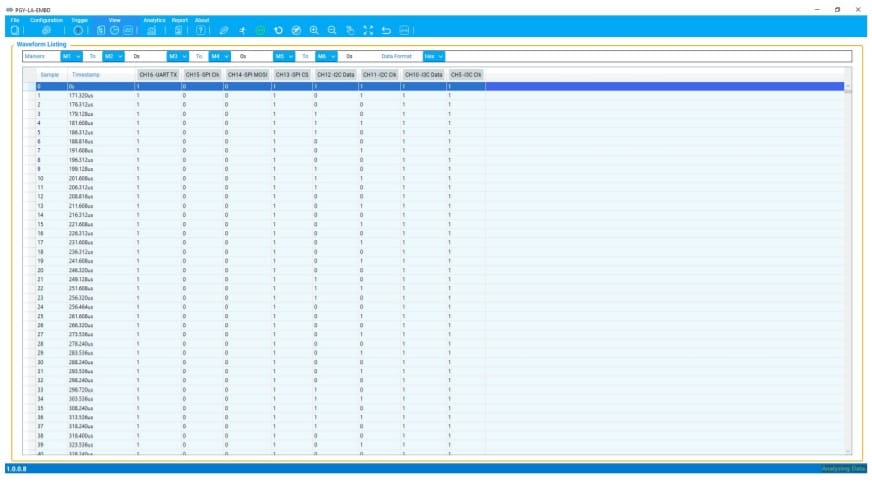

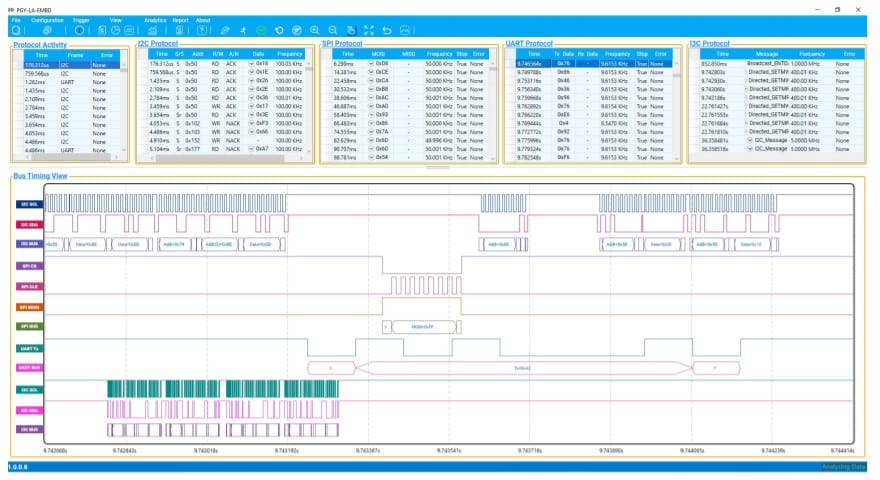

Las múltiples vistas de dominio proporcionan la visión completa necesaria de la actividad de estado, temporización y protocolo de todas las interfaces compatibles. Los usuarios pueden configurar fácilmente el analizador para que muestre las vistas de temporización, lógica y decodificación de protocolos para facilitar la comprensión del diseño. se pueden establecer varias condiciones de activación mediante el menú de configuración para capturar la actividad de temporización y protocolo en eventos específicos. Los resultados decodificados pueden verse en las ventanas de temporización, lógica y lista de registro con autocorrelación. Esta completa visión de la información la convierte en una de las mejores del sector y proporciona una solución fácil de usar para depurar la actividad del protocolo de la interfaz embebida y analizar los problemas de temporización. Los cursores múltiples ayudan a los desarrolladores a examinar los detalles del rendimiento de su diseño.

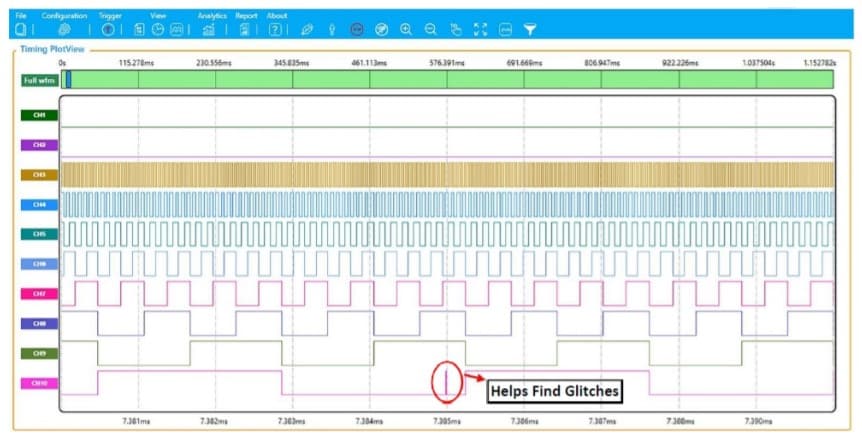

Vista de temporización

La Vista de Temporización es una función exclusiva del PGY-LA-EMBD que permite a los diseñadores obtener información detallada sobre la temporización de sus señales. La Vista de temporización utiliza una señal de reloj interna para representar la forma de onda. La selección flexible de la frecuencia de muestreo permite a los desarrolladores investigar los fallos que pueden causar problemas en el funcionamiento de sus diseños. La función de agrupación permite a los desarrolladores agrupar diferentes señales relacionadas para una mejor visualización y análisis. Las funciones de marcado y zoom facilitan el análisis de los errores de temporización. La posibilidad de analizar cualquier punto del conjunto de datos adquiridos facilita la depuración y el análisis durante un largo periodo de adquisición.

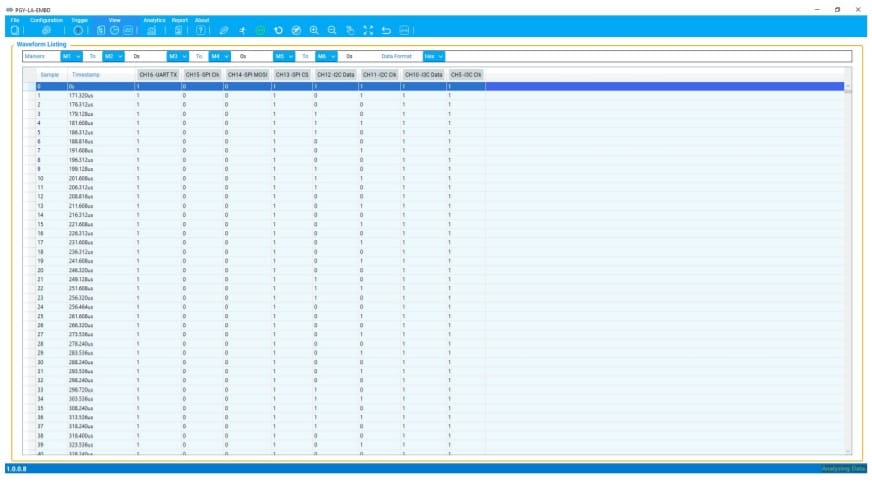

Vista de estado/Vista de listado de formas de onda

Vista de descodificación de protocolos

La ventana Actividad del protocolo muestra la información de los paquetes descodificados en cada estado y todos los detalles de los paquetes con información de errores en los mismos. Esto proporciona a los equipos de desarrollo una visión a nivel de sistema. Las ventanas individuales de descodificación de protocolos se basan en las interfaces seleccionadas y garantizan una fácil visualización para los equipos de desarrollo. La trama seleccionada en la ventana de listado de protocolos se autocorrelaciona en la vista de temporización para mostrar la información de temporización del paquete. Los errores de protocolo se resaltan para llamar fácilmente la atención de los desarrolladores.

Potentes funciones de activación

Informe

Se puede generar un informe en formato PDF o CSV con toda la información de la señal, gráficos y detalles personalizados, como el nombre de la empresa, el logotipo, el nombre del comprobador, la fecha y la hora, para garantizar que los diseñadores puedan documentar todos los detalles y compartir el informe.

Garantía

El hardware y el software están cubiertos por una garantía de un año. Las sondas están cubiertas por una garantía de tres meses para todos los defectos de fabricación

Especificación

| Especificación |  |

|---|---|

| Número de canales | 16 canales lógicos |

| Velocidad de estado | 1GS/s (adquisición asíncrona) |

| Velocidad de temporización | Sondas activas soldadas |

| Número de soporte de reloj de estado | Segundo, flexibilidad para muestrear en flanco ascendente o descendente |

| Longitud del conjunto de datos | Transmisión inteligente y continua de datos al HDD/SSD del ordenador central |

| Soporte de nivel de tensión | 0 a 5 V con flexibilidad para definir el umbral lógico |

| Gráfico de forma de onda | Muestra formas de onda con diagrama de bus configurable flexiblemente |

| Vista de lista | Lista todas las muestras de datos en cada punto de muestra |

| Disparo por LA | Disparo por patrón, disparo por ancho de pulso, disparo por retardo |

| Soporte de decodificación de protocolos | I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE |

| Descodificación simultánea de I2C, SPI, UART | Sí, conecta el bus I2C, SPI y UART al analizador lógico. Captura y muestra simultáneamente los datos del bus Vista correlacionada en el tiempo con las formas de onda temporales correspondientes. |

| Vista de protocolo con vista de temporización (PA+LA) | Muestra simultáneamente los datos decodificados del protocolo con alta frecuencia de muestreo y formas de onda de temporización |

| Soporte API | Soporte para automatizar el funcionamiento con Python y C++ |

| Tipo de conexión | Sonda voladora con conectores #16 Pinzas de prueba Micro Grabber como accesorios opcionales |

| Disparadores externos | Conector SMA de salida de disparo |

| Marcadores | Seis, con información delta entre dos marcadores. |

| Llamadas | Vista de temporización Vista de lista de estado/lógica/señal Vista de protocolo Diagrama de bus para mostrar paquetes de protocolo con diagrama de temporización Parcela Disparo automático - Por defecto (Disparo en cualquier paquete) |

| Disparo de protocolo | Disparo por patrón Disparo consciente del protocolo- UART: bit de inicio, bit de paridad, datos SPI: datos MOSI, datos MISO I2C: bit START, dirección, datos, dirección más datos, ACK, NACK, START repetido, bit STOP Disparo por parámetro de temporización: ancho de pulso (positivo o negativo) Disparo por retardo. |

| Duración de la adquisición | Transmisión inteligente de los datos de registro al HDD/SSD anfitrión. |

| Informe | Generación de informes en formato PDF y CSV |

| Conectividad con el host | USB 3.0 Tipo-C |

| Dimensiones | 115 mm x 90 mm x 25 mm |

| Peso | 300 g |

.jpg)

.jpg)

.jpg)

.jpg)